数字逻辑与数字系统复习

从零到一

进制

十进制: D

二进制: B

八进制: O

十六进制: H

位置计数法

R进制: $(N){R} = (K{n-1}K_{n-2}…K_{1}K_{0}.K_{-1}K_{-2}…K_{-m})_{R}$

- 多项式表示: $(N){R} =(\Sigma K{i}*R^{i})_{R}$

- 权: $R^{i}$

- 基数: R

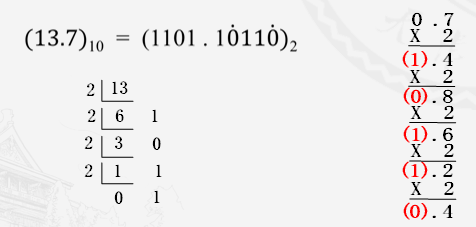

进制转换

- $\alpha \rightarrow 10 $

- $10 \rightarrow \beta$

- 整数部分: 基数除法

- 小数部分: 基数乘法

- $\alpha \rightarrow \beta \rightarrow 10$

- 特殊情况: 16, 2, 8进制的相互转换

编码

补码

- 二进制由原码获得补码的方法

- 正数: 原码与补码相同.

- 负数: 由原码数值位取反加1获得, 符号位不变.

增加位宽

- 零扩展

- 将零一直拷贝到最高位

- 负数值发生变化

- 符号位扩展

- 将符号位一直拷贝到最高位

- 数值不变

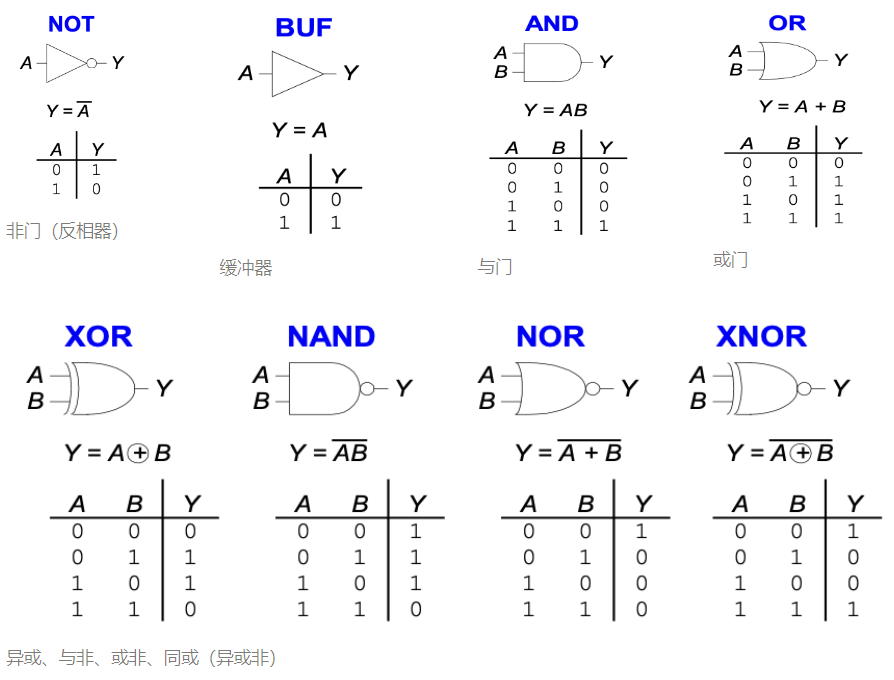

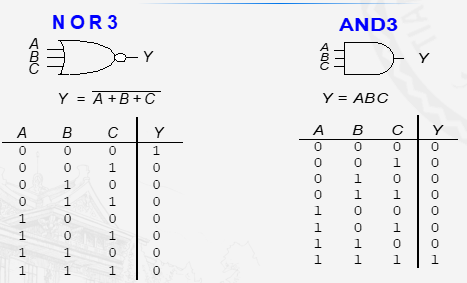

逻辑门

组合逻辑设计

概论

-

组合逻辑电路

- 任一时刻的输出仅由该时刻的输入信号决定

- 无记忆的, 与电路状态无关

-

时序逻辑电路

- 任一时刻的输出由该时刻的输入和电路该时刻的状态共同决定

- 有记忆的, 与电路状态有关

-

组合逻辑电路

- 每个电路模块都是一个组合逻辑电路

- 每个电路的输入只来自于一个节点的输出:

- 每个电路结点或者是电路的输入或者是只连接电路模块的一个输出端

- 电路中不包含回路

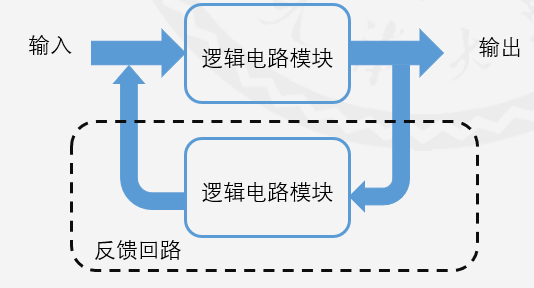

时序逻辑设计

引言

- 时序逻辑电路的输出由当前时刻的输入和之前时刻的输入共同决定

- 一些基本概念

- 状态:用于解释电路未来行为所需的信息

- 锁存器与触发器:用于存储1比特状态的模块

- 同步时序逻辑电路:一类由组合逻辑和和一组表示电路状态的触发器所构成的电路

- 时序逻辑电路特征

- 按照一定的输入输出时序实现功能

- 电路内部具有短期记忆

- 在输出与输入之间具有反馈回路

时序问题

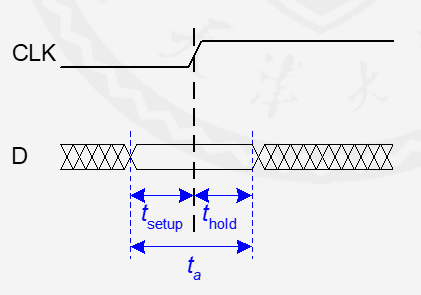

- D 触发器在时钟的有效边沿(上升沿/下降沿)对输入D采样, 并复制给Q. 此时D必须处在一个稳定的状态, 为0或为1, 否则会产生亚稳态.

- 建立时间: $t_{setup} = $ 在时钟有效边沿到来前输入信号所需要的稳定时间

- 保持时间: $t_{hold} = $ 在时钟有效边沿到来后输入信号所保持稳定时间

- 孔径时间: $t_a = $在时钟边沿附近输入信号需要保持稳定的总时间

- $t_a = t_{setup} + t_{hold}$

指令集体系结构

MIPS指令类型

I型

- 数据通路:完成对指令中操作数的运算、存储等处理工作

- 控制通路:从数据通路中接收指令,并对其进行翻译以告知数据通路如何处理

数字逻辑与数字系统复习

http://zqizhang.github.io/2022/08/23/数字逻辑与数字系统复习/